# Implementasi HEVC Codec pada Platform Berbasis FPGA

# Oktavia Ayu Permata<sup>1,\*</sup>, Wirawan<sup>1</sup>

1 Jurusan Teknik Elektro, Institut Teknologi Sepuluh Nopember, Surabaya, Indonesia \* oktapermata@gmail.com

Abstrak. Zynq 7000 terdiri dari dua elemen AP SoC yaitu *Processing System* (PS) dan *Programmable Logic* (PL). AP SoC dapat digunakan untuk implementasi algoritma pemrosesan video baik sebagai program software yang berjalan pada PS Zynq 7000 AP SoC atau sebagai akselerator hardware di dalam AP SoC berbasis PL. Pada paper ini, HEVC codec diimplementasikan sebagai program software yang berjalan pada PS Zynq 7000. Implementasi dilakukan pada bagian dual core prosesor ARM Cortex A9 dengan bantuan cross compiler. Cross compiler digunakan untuk mengompile HM *reference software* ke dalam bentuk binary supaya bisa dibaca oleh board dengan bantuan SDK. Hasil menunjukkan bahwa HM *reference software* dapat berjalan baik pada PS Zynq 7000. Beberapa parameter yang dapat dianalisa berdasarkan sampel konfigurasi yang digunakan meliputi PSNR, waktu yang diperlukan untuk encoding dan decoding data, serta perbandingan ukuran file video setelah di kompres.

Kata Kunci: HEVC, ARM, Zynq 7000

#### 1. Pendahuluan

High Efficiency Video Coding (HEVC) telah di desain sebagai standar terbaru untuk beberapa aplikasi video coding dan memiliki peningkatan kemampuan yang cukup signifikan dibandingkan dengan standar sebelumnya [1]. Salah satu langkah untuk mengadopsi standar baru dalam industri adalah dengan menguji kemampuan standar baru tersebut pada platform yang sesuai, berdasarkan aplikasi yang akan dikembangkan untuk produk tertentu. Dalam hal ini, HEVC codec di implementasikan pada Zynq 7000 AP SoC, sebuah platform berbasis FPGA dan prosesor dual-core ARM Cortex A9 yang terintegrasi dalam satu chip.

Permintaan yang tinggi pada konten *ultra high definition* (UHD) dan beberapa aplikasi multimedia juga melatar belakangi pengerjaan proyek ini. Karena peningkatan resolusi video maka software tidak lagi mampu melakukan encoding video secara real time. Salah satu solusi untuk mengatasi hal tersebut adalah dengan membuat algoritma kompresi secara paralel dan mengeksekusi program pada GPU atau hardware. Masalah dengan kompresi video atau kompresi secara umum terletak pada algoritma kompresi yang hanya bekerja optimal jika dilakukan secara serial [2]. Proses serial memungkinkan kompresor untuk mempelajari keputusan dari hasil sebelumnya sampai menghasilkan ukuran file video yang lebih kecil. Tetapi, beberapa bagian dari encoder video dapat ditangani secara paralel seperti *motion estimation* dan *intra prediction* [4]. Oleh karena itu, solusi ideal adalah dengan memiliki sebuah *software / hardware co-design* dimana stuktur utama tetap dalam bentuk serial dengan banyak asistensi dari hardware yang dikerjakan secara paralel. Dengan menggunakan Zynq 7000 AP SoC yang memiliki kemampuan untuk bekerja secara serial dan paralel, pemrosesan pada hardware dan software dapat dikombinasikan secara efisien.

Mengingat kompleksitas dari sistem yang akan dibuat dan juga komputasional yang tinggi dari sisi HEVC codec, langkah awal dalam pengerjaan proyek ini adalah dengan menggunakan *open-source* dari HEVC yang dikenal sebagai HM (HEVC test Model) *reference sotfware*. Software ini kemudian dapat dijalankan pada internal prosesor Zynq. Zynq memiliki dua bagian utama yaitu *processing system* (PS) yang mengatur kinerja dari prosesor dual-core ARM Cortex A9 dan *programmable logic* (PL) yang merupakan inti dari FPGA. Pada makalah ini hanya dibahas pada bagian PS. HM *reference software* di implementasikan pada prosesor dual-core ARM Cortex A9 dengan bantuan *cross compiler* dan SDK. Sistem dijalankan pada Linux OS. Selanjutnya, hasil dari encoder dan decoder dapat dianalisa berdasarkan parameter yang dapat diubah – ubah pada HM *reference software*. Hasil

menunjukkan ukuran file video sebelum dan setelah di kompres dengan HEVC, waktu yang diperlukan untuk menjalankan program, dan kualitas dari video.

# 2. Zynq 7000 AP SoC

System on Chip (SoC) merupakan bidang yang berkembang sangat cepat pada desain VLSI (Very Large Scale Integrated circuits). Sistem yang kompleks dapat di integrasikan ke dalam sebuah chip melalui metodologi desain SoC untuk mencapai daya rendah, biaya rendah, dan kecepatan yang tinggi dibandingkan dengan desain board tradisional [2]. Dibandingkan dengan ASIC, SoC yang berbasis FPGA adalah reconfigurable yang berarti bahwa desain pada device dapat dimodifikasi sesuai dengan keperluan. Hal tersebut membantu akselerasi dan mempermudah pengembangan dari suatu sistem. Zynq-7000 berbasis pada arsitektur Xilinx All Programmable (AP) System on Chip (SoC). FPGA terintegrasi dengan dual core ARM Cortex A9 berbasis processing system (PS) dan 28 nm Xilinx programmable logic (PL) pada satu device. PS tidak hanya terdiri dari prosesor ARM, tetapi juga satu set prosesing yang membentuk Application Processing Unit (APU), dan peripheral interface yang lain, cache memori, memori interface, interconnect, dan clock pembangkit circuit [3].

Dari perspekstif pemrograman, dukungan untuk instruksi ARM disediakan oleh Xilinx *Software Development Kit* (SDK) yang meliputi semua komponen yang diperlukan untuk mengembangkan software yang akan di implementasikan pada prosesor ARM. *Compiler* mendukung ARM dan pengaturan perintah *Thumb* (16-bit atau 32-bit), sejalan dengan 8-bit Java *bytecode* (yang dipakai pada *Java Virtual Machine*) pada kondisi yang ideal.

#### 3. Desain Sistem

Pada bagian ini, desain sistem meliputi dua bagian: desain Zynq PS dan desain HEVC codec.

## A. Desain Zyng PS

Berdasarkan target board Xilinx Zynq ZC702, desain PS di realisasikan melalui *cross compile* antara HM *reference software* yang *support* FFmpeg dengan board Zynq. HM *reference software* di *compile* pada Ubuntu 14.04 LTS, menghasilkan code berbentuk binari yang dapat dibaca dan di *run* pada board dengan bantuan SDK. Secara singkat desain PS dapat digambarkan sebagai berikut:

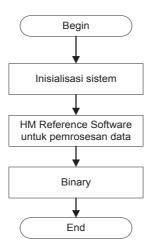

Gambar 1. Proses desain PS

Dari gambar 1, binari kemudian di copy di board Zynq. SDK yang berfungsi sebagai *profiling* data, digunakan untuk membantu prosesor ARM membaca data dan menjalankan perintah pemrosesan HEVC codec menggunakan code yang sudah dibangkitkan dalam bentuk binari. HM *reference software* menghasilkan 8 binari yang dapat dipakai untuk pemrosesan video. Pada makalah ini, dipakai

2 binari yaitu *TAppEncoderStatic* yang merupakan versi keluaran dari H.265 / encoder HEVC dan *TAppDecoderStatic* yang merupakan versi keluaran dari H.265 / decoder HEVC.

#### B. Desain HEVC codec

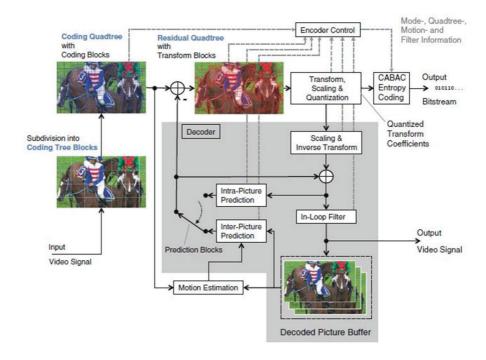

Dengan menggunakan HM *reference sotfware*, maka secara langsung desain HEVC menggunakan desain standar proses encoding dan decoding HEVC. Standar HEVC di desain berdasarkan prinsip *hybrid video coding*. Gambar 2 menunjukkan blok diagram dari sebuah blok berbasis *hybrid video encoder* dengan beberapa karaterisktik dari HEVC berdasarkan novel konsep untuk partisi blok.

Dari gambar 2, sebuah gambar dipartisi kedalam blok kemudian masing – masing blok diprediksi menggunakan *inter prediction* atau *intra prediction*. Ketika metode prediksi sebelumnya hanya menggunakan sampel yang telah di decode dalam gambar yang sama sebagai acuan, HEVC menggunakan blok dari gambar yang sudah di decode sebagai acuan. Karena *inter-picture prediction* secara tipikal mengkompensasi gerakan dari objek nyata antara gambar dari urutan video, hal tersebut juga direferensikan sebagai *motion-compensated prediction*. Ketika *intra-picture prediction* mengekploitasi redundansi spatial antara blok tetangga di dalam sebuah gambar, *motion-compensated prediction* menggunakan ukuran yang besar dari redundansi temporal antara gambar. Dalam kasus yang sama, hasil dari prediksi eror yang diperoleh dari perbedaan antara blok asli dengan blok hasil prediksi, ditransmisikan dengan coding transform yang mengeksploitasi redundansi spatial di dalam sebuah blok yang terdiri dari transform linier yang tidak saling berkorelasi, kuantisasi scalar dari koefisien transform, dan entropi coding dari hasil transform level koefisien [1].

Gambar 2. Blok diagram dari encoder HEVC dengan built-in decoder (warna abu - abu)

#### 4. Implementasi

Pada bagian ini, implementasi dilakukan melalui tiga tahap meliputi: HM reference software, cross compile, dan SDK.

#### A. HM reference software

Mempertimbangkan kompleksitas coding dan pemrosesan secara paralel pada standar HEVC, maka digunakan HM *reference software* sebagai langkah awal. Untuk melakukan encode dan decode sebuah file video, digunakan HM encoder versi 16.06. HM *reference software* digunakan untuk menyediakan dan mendemonstrasikan kemampuan dari standar H.265. Code dibuat dalam bahasa pemrograman C.

Sebelum dapat menggunakan HM *reference software*, proyek file yang tersedia harus di instal dan di compile. Terdapat beberapa macam proyek file yang dapat dieksekusi untuk pengembangan sistem. HM *reference software* juga menyediakan banyak contoh konfigurasi yang dapat digunakan untuk mengolah file video. Pada makalah ini digunakan encoder intra main.cfg sebagai contoh konfigurasi.

#### B. Cross compile

Cross compile adalah compiler yang mampu membuat code yang dapat dieksekusi oleh sebuah platform selain dari compiler yang sedang digunakan. Untuk makalah ini, cross compiler diperlukan untuk melakukan compile pada HM reference software yang support FFmpeg pada Ubuntu 14.04 LTS dan membangkitkan code yang bisa dijalankan pada board ZC702. GCC dan cross compilation diperlukan untuk tujuan tersebut. GCC adalah koleksi free software dari compiler, dapat diatur untuk cross compile dan mendukung beberapa platform dan bahasa pemrograman.

## C. Software Development Kit (SDK)

Xilinx tool merupakan alat yang digunakan untuk mempermudah desain hardware maupun software. Sesuai dengan tipe Zynq yang dipakai yakni ZC702, *Vivado Design Suite* digunakan untuk mempermudah pengerjaan desain sistem. Vivado dan SDK merupakan tool yang terdapat pada *Vivado Design Suite*. Kedua tool tersebut bisa dikatakan tool terpenting dalam *Vivado Design Suite* karena digunakan untuk desain hardware dan desain software.

Vivado merupakan tool pengembangan untuk membuat sistem hardware yang merupakan bagian dari desain SoC, seperti prosesor, memori, *peripheral*, interface external, dan koneksi bus. SDK adalah *software design suite* berbasis pada platform Eclipse, yang mencakup *driver support* untuk semua Xilinx IP, GCC *library* yang *support* ektensi untuk ARM dan NEON menggunakan bahasa C dan C++, dan tool untuk *debugging* dan *profiling*. Dengan SDK, software dapat diuji meskipun sedang berjalan pada target hardware platform.

## 5. Hasil Implementasi

Pada bagian ini, hasil implementasi dibandingkan antara hasil run pada Linux dan PS Zynq. Hasil implementasi meliputi perbandingan ukuran file video setelah di kompres, waktu proses encoding dan decoding video, serta kualitas dari video hasil kompres dengan HEVC. File video yang digunakan berupa format YUV, memiliki resolusi 1920x1080 pixel, dan fps 24 yang disesuaikan dengan fps minimal untuk HD video. File video YUV ini selanjutnya diproses untuk encoding dan decoding menggunakan standar HEVC. Dua file video yang digunakan yaitu:

- 1. Kimono.yuv

- 2. Sintel trailer.yuv

## A. Hasil pada Linux

Konfigurasi file video yang digunakan adalah encoder intra main.cfg dengan QP = 32.

Tes Waktu Ukuran Jumlah Waktu Ukuran Ukuran video video frame decoding encoding encoding decoding (detik) (detik) 746,5 MB 240 frame 2167,291 18,381 8,6 MB 746,5 MB Video 1 Video 2 3.9 GB 1253 frame 10151,592 52,21 10,9 MB 3,9 GB

Tabel 1. Tes HEVC di Linux

Tabel 2. PSNR Video 1

| Y-PSNR U-PSNR |         | V-PSNR  | YUV-PSNR |  |

|---------------|---------|---------|----------|--|

| 38,9512       | 41,1150 | 42,0501 | 39,5547  |  |

# B. Hasil pada PS Zynq

Tabel 3. Tes HEVC di PS Zyng

| Tes<br>video | Ukuran<br>video | Jumlah<br>frame | Waktu<br>encoding<br>(detik) | Waktu<br>decoding<br>(detik) | Ukuran<br>encoding | Ukuran<br>decoding |

|--------------|-----------------|-----------------|------------------------------|------------------------------|--------------------|--------------------|

| Video 1      | 746,5 MB        | 240 frame       | 1167,211                     | 17,301                       | 8,6 MB             | 746,5 MB           |

| Video 2      | 3.9 GB          | 1253            | 9151,522                     | 50,12                        | 10,9 MB            | 3,9 GB             |

|              |                 | frame           |                              |                              |                    |                    |

#### Tabel 4. PSNR Video 1

| Y-PSNR  | U-PSNR  | V-PSNR  | YUV-PSNR |  |

|---------|---------|---------|----------|--|

| 38.8394 | 41.9582 | 39.5621 | 38.4775  |  |

## 6. Kesimpulan

Makalah ini menyajikan implementasi HEVC codec pada Zynq 7000 yang berbasis pada sistem FPGA dan dibahas secara khusus pada bagian PS. Dari hasil yang diperoleh, HM *reference software* dapat bekerja baik pada board Zynq ZC702. Semakin banyak frame yang digunakan, semakin banyak waktu yang diperlukan untuk proses encoding. Dengan membandingkan hasil dari waktu yang diperoleh pada proses encoding dan decoding, PS Zynq dapat melakukan pemrosesan data lebih cepat dibandingkan Linux. Hal tersebut memungkinkan sistem ini digunakan untuk streaming video realtime, meskipun terdapat beberapa faktor yang perlu dioptimalkan pada kinerja sistem.

Secara subjektif, dengan meminta pendapat dari beberapa rekan Lab Telekomunikasi Multimedia, video yang dihasilkan dengan kompresi HEVC tidak begitu jauh berbeda dengan video asli yang digunakan dengan standar H.264. Untuk memenuhi kebutuhan streaming video real time, studi lebih lanjut diperlukan pada desain sistem untuk mendapatkan hasil yang lebih optimal. Penelitian selanjutnya akan dilakukan untuk *hardware/software co-design*.

### 7. Daftar Referensi

- [1] Sze Vivienne, Budagavi Madhukar, Sullivan GJ. High Efficiency Video Coding (HEVC) Algorithm and Architecture. Springer, 2014.

- [2] Stewart RW, Endewitz MA, Elliot RA, Crockett LH. *The Zynq Book*. Strathclyde Academic Media, 2014.

- [3] Li Z, Li J, Zhao Y, Rong C, Ma J., "A SoC Design and Implementation of H.264 Video Encoding System Based on FPGA", 2014 Sixt International Conference on Intelligent Human –Machine Systems and Cibernatics, IEEE, 2014.

- [4] Xilinx Inc., UG585: Zynq 7000 All Programmable SoC Technical Reference Manual, 2015, http://www.xilinx.com/.

- [5] Wien Mathias. High Efficiency Video Coding. Coding Tools and Specification. Springer, 2014.

- [6] Xilinx Inc., UG850: ZC702 Evaluation Board for the Zynq-7000 XC7Z020 All Programmable SoC User Guide, 2015, <a href="http://www.xilinx.com/">http://www.xilinx.com/</a>